メモリスタ

テンプレート:Distinguishテンプレート:Infobox electronic component

メモリスタ (またはメモリスター。テンプレート:Lang-en, テンプレート:IPAc-en; メモリ抵抗器 のかばん語) は、電荷とテンプレート:Ill2に関係する非線形テンプレート:Ill2電気部品である。通過した電荷を記憶し、それに伴って抵抗が変化する受動素子である。過去に流れた電流を記憶する抵抗器であることからメモリスタ (テンプレート:Lang) と名づけられた。

1971年にテンプレート:仮リンクによって言及と命名がなされ、これにより、抵抗器、コンデンサ、インダクタも含む基本的な電気部品の理論上のカルテットが完成した[1]。抵抗器、キャパシタ、インダクタに次ぐ新たな受動素子であるので、“第4の回路素子” と呼ばれる。

テンプレート:仮リンクとテンプレート:Ill2は後にこの概念をメモリスティブ体系に一般化した[2]。理想的なメモリスタ部品の主要な特性を複数の在来型の部品からなる回路で模倣するようなシステムも、一般にメモリスタと呼ばれる。 このようなメモリスタ・システム技術はいくつか開発されており、特にReRAMがその1例である。

電子デバイスのメモリスティブ特性の特定は論争を呼んでいる。実験的には、理想的なメモリスタはまだ実証されていない[3][4]。

基本的な電気部品として

蔡は1971年の論文で、非線形抵抗器 (電圧対電流)、非線形コンデンサ (電圧対電荷)、および非線形インダクタ (磁束鎖交対電流) の間に理論上の対称性を特定した。この対称性から、彼は磁束と電荷を結び付ける第四の基礎的非線形回路要素の特性を推測し、これをメモリスタと呼んだ。線形 (または非線形) 抵抗器とは対照的に、メモリスタは過去の電圧または電流の記憶を含め、電流と電圧の間にダイナミックな関係を持っている。他の科学者は、テンプレート:Ill2のテンプレート:Ill2のようなダイナミックメモリ抵抗器を提案していたが、蔡は数理的普遍性を導入した。

由来と特性

メモリスタは、通過した電荷と端子間の磁束鎖交が非線形関数関係であるような素子と定義される。すなわち、と表わされる[5]。磁束鎖交は、インダクタの回路特性から一般化される。ここでは磁場を表すものではなく、その物理的意味については以下で説明する。 記号はすなわち、電圧の時間積分と見なすことができる[6]。

との関係において、一方の他方に対する導関数は、一方または他方の値に依存する。そしてそれゆえ、それぞれの導関数は電荷を伴なう磁束の変化の電荷依存率を述べるメモリスタンス関数によって特徴づけられる。磁束を電圧の時間積分として、電荷を電流の時間積分として代入すると、より便利な形式が得られる:メモリスタを抵抗、キャパシタ、インダクタに関連付けるには、デバイスを特徴付ける項を分離し、常微分方程式として記述すると便利。

| 素子 | テンプレート:Ill2 (単位) | 常微分方程式 |

|---|---|---|

| 抵抗器(R) | 抵抗 (V / A, or Ω) | |

| キャパシタ(C) | 静電容量 (C / V, or ファラド) | |

| インダクタ(L) | インダクタンス (Wb / A, or ヘンリー) | |

| メモリスタ(M) | メモリスタンス (Wb / C, or Ω) |

上記の表は、、、およびの微分の有意義な比率を全てカバーする。はの導関数であり、またはの積分であるため、をに、またはをに関連付けることができるデバイスはない。このことから、メモリスタは電荷に依存する抵抗であると推測できる。もしが定数の場合、オームの法則が得られる。ただし、が自明でない場合、とは時間とともに変化する可能性があるため、方程式は同等ではない。時間の関数として電圧を解くと、が得られる。この方程式はが電荷によって変化しない限り、メモリスタが電流と電圧の間で線形関係を定義することを示している。非ゼロ電流は時間変化する電荷を意味する。交流電流は(しかしながら)、の最大変化によってにテンプレート:Ill2変化を引き起こさない限りテンプレート:Mdash正味の電荷の移動を伴わずに測定可能な電圧を誘導することにより回路動作の線形依存性を明らかにすることができる。

さらに、電流が印加されない場合、メモリスタは静的である。 の場合、であり、は定数であることがわかる。これはメモリー効果の本質である。

同様に、をメモダクタンスとして定義できる[5]。電力消費特性、これは抵抗器の式を思い出させる。がほとんど変化しない限り(交流下など)、メモリスタは定抵抗器のように見える。もしもが敏速に増加すると(しかしながら)電流と電力消費は急速に停止する。

は、のすべての値に対して正になるように物理的に制限される (デバイスが受動的であり、あるで超伝導状態にならないと仮定する)。 負の値は、交流で動作するときにエネルギーを永続的に供給することを意味する。

モデル化と検証

メモリスタ機能の性質を理解するためには、テンプレート:Ill2の概念から始めて、基本的な回路理論の概念についてある程度の知識があると役に立つ[7]。

エンジニアや科学者が物理システムを元の形で分析することはめったにない。代わりに、彼らはシステムの挙動を近似するモデルを構築する。モデルの挙動を解析することで、彼らは実際のシステムの挙動を予測することを望んでいる。モデルを構築する主な理由は、通常、物理システムが複雑すぎて実際の分析に対応できないからである。

20世紀には、研究は研究者がメモリスティブ特性を認識していないデバイスで行われた。このため、そのようなデバイスはメモリスタとして認識されるべきであるという提案が提起された[7]。PershinとDi Ventra[3]は、理想的なメモリスタが実際に存在するのか、それとも純粋に数学的な概念であるのかについての長年の論争の解決に役立つテストを提案した。

2008年以降の研究の大部分はこの分野に集中しているため、この記事の残りの部分では主にReRAMデバイスに関連するメモリスタについて説明する。

超電導メモリスタ部品

Paul Penfield博士は、1974年のMIT技術報告書[8]の中で、ジョセフソン接合に関連してメモリスタについて言及している。これは回路デバイスの文脈における「メモリスタ」という単語の初期の使用例であった。

ジョセフソン接合を通る電流の項の1つは次の式のように表され: には物理的な超電導材料に基づく定数が、には接合部両端間の電圧が、には接合部を流れる電流が当て嵌まる。

20世紀後半を通じて、このジョセフソン接合における位相依存コンダクタンスに関する研究が行われた[9][10][11][12]。この位相依存コンダクタンスを推論するためのより包括的なアプローチが、2014年にPeottaとDiVentraの独創的な論文で登場した[13]。

メモリスタ回路

理想的なメモリスタを研究することは現実的には難しいため、メモリスタを使用してモデル化できるその他の電気デバイスについて話すことにする。メモリスティブ・デバイス (システム) の数学的記述については、#理論を参照されたし。

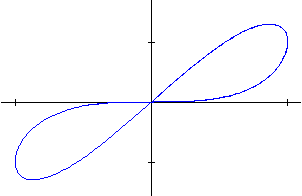

放電管は、伝導電子の数の関数である抵抗(値)で、メモリスティブ・デバイスとしてモデル化できる[2]。は放電管の両端の電圧、はそこを流れる電流、そしては伝導電子の数である。単純なメモリスタンス関数はである。 そしてはチューブの寸法と充填ガスに依存するパラメータである。メモリスティブな挙動の実験的な特定は、平面における「ピンチ化ヒステリシス・ループ」である。一般的な放電管のこのような特性を示す実験については、「物理メモリスタのリサジュー図(A physical memristor Lissajous figure)」(YouTube)を参照されたし。動画では物理メモリスタのピンチ化ヒステリシス特性における偏差をどのように理解するかも図解している[14][15]。

サーミスタはメモリスティブ・デバイスとしてモデル化できる[15]。は材料定数であり、はサーミスタの絶対体温であり、は周囲温度 (温度単位は両方ともケルビン)であり、はにおける低温(側)抵抗(値)を示し、は熱容量であり、そしてはサーミスタの損失定数(熱放散定数)である。

ほとんど研究されていない基礎的な現象は、pn接合におけるメモリスティブな挙動である[16]。メモリスタはダイオードベースの電荷蓄積効果を模倣する上で重要な役割を果たし、また(順方向過渡時に非常に重要な)導電率変調現象にも関与する。

批評

2008年に、テンプレート:仮リンクのチームは二酸化チタンの薄膜の分析に基き、その結果ReRAMデバイスの動作をメモリスタの概念に結び付けることができる、蔡のメモリスタについての実験的証拠を発見した。HP研によると、メモリスタは次のように動作する: メモリスタのテンプレート:Ill2は一定ではなく以前デバイスに流れた電流に依存し、すなわち、この現在の抵抗は以前にどれだけの電荷がそこを通って、どの方向に流れたかによって決まり; デバイスはその履歴テンプレート:Mdashいわゆる不揮発性特性テンプレート:Mdashを記憶する[17]。電力供給がオフになるとき、メモリスタは再度電源が入るまで自身の直近の抵抗(値)を記憶する[18][19]。

HP研の結果は科学雑誌Nature に掲載された[18][20]。この主張を受けて、蔡少棠は「メモリスタの定義は抵抗スイッチング効果に基く2端子不揮発性メモリデバイスのあらゆる形式をカバーするように一般化できる」と主張している[17]。蔡はまた「メモリスタは既知の中で最も古いテンプレート:Ill2であり、その効果は抵抗器、コンデンサ、そしてインダクタよりも古い」とも主張した[21]。本物のメモリスタが物理的な現実において実際に存在し得るのかに関しては(しかしながら)いくつかの深刻な疑問がある[22][23][24][25]。それに加えて、いくつかの実験的証拠では抵抗スイッチングメモリにおける非受動的テンプレート:Ill2効果が観察できるため蔡の一般論と矛盾する[26]。そのような理想的または一般的なメモリスタが実際に存在するのか、それとも純粋に数学的な概念であるのかを分析するため、PershinとDi Ventraによって簡単なテストが提案された[27]。今までのところ、テストを合格できる実験用の抵抗スイッチングデバイス (ReRAM) はないようである[27][28]。

これらのデバイスは、ナノエレクトロニクス メモリデバイス、コンピュータロジック、そしてニューロモルフィック/ニューロメモリスティブ・コンピュータアーキテクチャでの応用を企図されている[29][30]。2013年に、ヒューレット・パッカードのマーティン・フィンクCTOは、「メモリスタ・メモリは早ければ2018年にも市販される可能性がある」と示唆した[31]。2012年3月に、テンプレート:仮リンクとミシガン大学の研究者チームは、CMOSチップ上に構築された最初の機能するメモリスタ・アレイを発表した[32]。テンプレート:External media1971年の当初の定義によれば、メモリスタは4番目の基本回路要素であり、電荷と磁束鎖交の間に非線形関係を形成する。2011年に蔡は、より広い、抵抗スイッチングに基づく全ての2端子不揮発性メモリデバイスを含む定義を主張した[17]。WilliamsはMRAM、相変化メモリそしてReRAMはメモリスタ技術であると主張した[33]。一部の研究者は、血液[34]や皮膚[35][36]などの生物学的構造が定義に適合すると主張した。他の人はテンプレート:仮リンクが開発中のメモリデバイスや他の形式のReRAMはメモリスタではなく、むしろ可変抵抗システムのより広範なクラスの一部であり[37]、そしてメモリスタの広義の定義はHPのメモリスタ特許を有利にする科学的に不当なテンプレート:Ill2である[38]と主張した。

2011年に、MeuffelsとSchroederは初期のメモリスタ論文の1つにイオン伝導に関する誤った仮定が含まれていることを指摘した[39]。2012年に、MeuffelsとSoniは、メモリスタの実現におけるいくつかの基本的な課題と難問について議論した[40]。彼らはNature の論文「行方不明のメモリスタが見つかった(The missing memristor found)」[18]で提示された電気化学モデリングにおいて、電圧または電流ストレス下での「金属テンプレート:MdashTiO2−xテンプレート:Mdash金属」構造の挙動に対するテンプレート:Ill2効果の影響が考慮されていなかったため、不備を指摘した。この批判は2013年にValovら(et al.)[26]によって参照された。

ある種の思考実験において、MeuffelsとSoniは[40]、さらに次のような深刻な矛盾を明らかにした: いわゆる不揮発性特性[17]を持つ電流制御メモリスタが物理的現実に存在する場合、その挙動はシステムの「情報」状態を変更するために必要な最小エネルギー量に制限を設けるランダウアーの原理に違反することになる。この批判は最終的にテンプレート:Ill2とPershinによって採用された[41]。

この文脈の中において、MeuffelsとSoniは[40]、基本的な熱力学的原理を次のように指摘した: 不揮発性情報ストレージにはシステムの異なる内部メモリ状態を相互に分離する自由エネルギー障壁の存在が必要であり; さもないと、一方が「中性の」状況に直面することになり、そしてシステムがちょうど熱ゆらぎの影響下にある場合、ある記憶状態から別の記憶状態へ勝手気ままに変動してしまうだろう。熱ゆらぎに対して保護されていない場合、内部メモリ状態は、状態の劣化を引き起こすいくつかの拡散ダイナミクスを示す[41]。自由エネルギー障壁は(したがって)ビット操作の低ビットエラー確率を保証するのに十分高くなければならない[42]。その結果として、とあるメモリデバイスにおけるビット値の意図的な変更について テンプレート:Mdash 必要なビットエラー確率に応じ テンプレート:Mdash エネルギー必要量には常に下限が存在する[42][43]。

メモリスティブ体系の一般概念において、定義方程式は次のとおり (#理論を参照): は入力信号であり、そしては出力信号が当て嵌まる。ベクトルはデバイスの内部メモリ状態の違いを説明する個の状態変数のセットを表す。は時間を伴う状態ベクトルの時間依存変化率である。

一方が単なる曲線当てはめを超え、そして不揮発性メモリ要素(例えば抵抗変化型メモリデバイス)の実際の物理モデリングを目指しているとき、前述の物理的な相関関係に常に注意を払う必要がある。提案されたモデルとその結果として得られる状態方程式の適切性をチェックするために、入力信号は、避けられない熱ゆらぎの存在を考慮する、確率項(※原文: stochastic term) (※最小二乗法の誤差項(error term)εに字面が似ているがξは違う(大分配関数))と重畳しうる。動的状態方程式の一般形は最終的に次のようになる:には、例えば、ホワイトガウス電流または電圧ノイズが当て嵌まる。ノイズに対するシステムの時間依存応答の解析的または数値的解析に基づいて、モデリング手法の物理的妥当性について決定を下すこと(例えば、システムは電源オフモードでもメモリの状態を保持できるかどうか?)が可能になる。

純正の電流制御メモリスタに関して、このような分析はDi VentraとPershin[41]によって行われた。提案された動的状態方程式には、このようなメモリスタが避けられない熱ゆらぎに対処できるようにする物理的メカニズムが提供されていないため、電流制御メモリスタは、電流ノイズの影響を受けると、時間の経過とともにその状態が不規則に変化する[41][44]。Di VentraとPershin[41]はその結果、抵抗 (メモリ) 状態が電流または電圧の履歴のみに依存するメモリスタは、避けられないジョンソン=ナイキスト・ノイズから自らのメモリ状態を保護できず、永続的な情報損失(いわゆる「確率的大惨事」)に悩まされると結論付けた。電流制御メモリスタは、したがって、物理的現実に固体デバイスとして存在することはできない。

前述の熱力学的原理は、さらに2端子不揮発性メモリデバイス (例えば「抵抗スイッチング」メモリデバイス (ReRAM))の動作をメモリスタの概念と関連付けることはできないことを暗示し、つまり、そのようなデバイスは、それ自体では電流または電圧の履歴を記憶できない。異なる内部メモリまたは抵抗状態の間の遷移は確率的な性質を持っている。状態{i}から状態{j}への遷移ついての確率は、両方の状態の間の自由エネルギー障壁の高さに依存する。遷移確率は、適切にメモリデバイスを駆動すること(すなわち、(たとえば)外部から印加されるバイアスを用いて、{i} → {j}の遷移間の自由エネルギー障壁を「下げる」こと)による影響を受ける可能性がしたがってある。

「抵抗スイッチング」イベントは、外部バイアスを特定の閾値を超える値に設定することによって簡単に強制できる。これは自明なケースであり、すなわち、{i} → {j}の遷移間の自由エネルギー障壁はゼロに減らされる。一方に閾値を下回るバイアスを印加する場合、デバイスが時間の経過とともに(ランダムな熱ゆらぎによって引き起こされる)切り替わる確率は依然として有限であるが、しかし テンプレート:Mdash確率過程を扱っているためテンプレート:Mdash スイッチング イベントがいつ発生するかを予測することは不可能である。これが、観測された抵抗スイッチング (ReRAM) プロセスすべての確率的性質の基本的な理由である。自由エネルギー障壁が十分に高くない場合、メモリデバイスは何もすることなくいっそ切り替わることも可能である。

2端子不揮発性メモリデバイスが明確な抵抗状態{j}にあることが判明した場合、(したがって) 現在のその状態と、前述のその電圧履歴との間に物理的な1対1の関係は存在しない。個々の不揮発性メモリデバイスのスイッチング挙動は、その結果、メモリスタ/メモリスティブ体系に対して提案されている数学的枠組み内では説明できない。

熱力学へのさらなる好奇心はメモリスタ/メモリスティブ デバイスは抵抗器のようにエネルギッシュに振る舞うはずであるという定義から生じる。このような機器に入力される瞬時電力は、テンプレート:Ill2として周囲に完全に放散され、そのため、ある抵抗状態から別の抵抗状態に移行した後、システムには余分なエネルギーが残らない。したがって、(たとえこれらの異なる状態が異なるデバイスの抵抗(それ自体はデバイスの材質の物理的変化によって引き起こされるに違いない)を生じさせたとしても)状態(U (V, T, xi))におけるメモリスタデバイスのテンプレート:Ill2は状態(U (V, T, xj))における場合と同じになる。

他の研究者は、線形テンプレート:Ill2の仮定に基づくメモリスタモデルは、セット時間(高抵抗から低抵抗へのスイッチング)とリセット時間(低抵抗から高抵抗へのスイッチング)の間の非対称性を考慮しておらず、且つ、実験データと一致するイオン移動度値が提供されてないことを指摘した。この欠陥を補うために非線形イオンドリフトモデルが提案されている[45]。

ReRAMの研究者による2014年の論文は、Strukov (HP) の初期/基本メモリスタ モデリング方程式は実際のデバイスの物理(学)をよく反映していないと結論付けた一方、PickettのモデルやMenzelのECMモデル (Menzelはその論文の共著者) などの後続の (物理ベースの) モデルには十分な予測可能性があるが、しかし計算量的には法外に高い。2014年現在、これらの課題のバランスをとるモデルの探索が続けられている; この論文ではChang氏とYakopcic氏のモデルが潜在的に優れた妥協案であると指摘している[46]。

テンプレート:Ill2(研究機関ガートナーの電気工学アナリスト) は「HPが自社のデバイスをメモリスタと呼んでいたのはいい加減であった一方、批評家たちは、それはメモリスタではないと学者ぶって言っていた。」とコメントした[47]。

実験的試験

蔡は、デバイスがメモリスタとして適切に分類されるかどうかを判断するための実験的試験を提案した[2]:

- 電圧テンプレート:Ndash電流平面におけるリサージュ曲線は初期条件とは関係なく、双極性の周期的な電圧または電流によって駆動されると、ピンチ化ヒステリシス・ループになる。

- ピンチ化ヒステリシス・ループの各突出部の面積は、強制信号の周波数が増加するにつれて縮小する。

- 周波数が無限大に近づくにつれて、ヒステリシス・ループは原点を通る直線に縮退し、その傾きは強制信号の振幅と形状に依存する。

蔡によれば[48][49]、ReRAM、MRAM、そして相変化メモリを含む、全ての抵抗スイッチング・メモリはこれらの基準を満たしており、メモリスタである。しかしながら、初期条件の範囲または周波数の範囲にわたるリサージュ曲線についてのデータの欠如が、この主張の評価を複雑にする。

実験的証拠は、酸化還元ベースの抵抗メモリ (ReRAM) には蔡のメモリスタ・モデルとは相反するテンプレート:Ill2効果が含まれることを示している。これはメモリスタ理論を正確なReRAMモデリングを可能にするために拡張または修正する必要があることを暗示している[26]。

理論

2008年に、テンプレート:仮リンク出身の研究者は、二酸化チタンの薄膜に基づくメモリスタンス関数についてのモデルを発表した[18]。 ≪ について、メモリスタンス関数は以下であると同定された: ここでは高抵抗状態を表し、は低抵抗状態を表し、は薄膜内のドーパントの移動度を表し、そしては膜厚を表す。HP研のグループは「非線形イオンドリフトおよび境界効果に帰因する実験の測定(結果)とメモリスタモデル間の差異を埋め合わせるためには『窓関数』が必要である」と指摘した。

スイッチとしての動作

一部のメモリスタについて、印加電流または電圧は抵抗に大きな変化を引き起こす。このようなデバイスは抵抗に望ましい変化を達成するために費やさなければならない時間とエネルギーを調べることによってスイッチとして特徴づけられる場合がある。これは印加電圧が一定のままであると仮定する。単一スイッチング・イベント中のエネルギー放散について解くと、メモリスタにとってからまでの時間内にからに切り替わるには、電荷がだけ変化しなければならないことが明らかになる。を代入し、定数にを代入すると、最終的な式が得られる。この電力特性はコンデンサ・ベースの金属酸化物半導体トランジスタの電力特性とは根本的に異なる。トランジスタとは異なり、電荷の観点からメモリスタの最終状態はバイアス電圧に依存しない。

Williamsによって説明されたメモリスタの種類は、その抵抗範囲全体にわたるスイッチング後、理想的ではなくなり、「ハードスイッチング・レジーム」とも呼ばれる、ヒステリシスを形成する[18]。もう一つの種類のスイッチは、周期的なを持ち、そのため一定のバイアスの下では、各オフ-オン・イベントの後にオン-オフ・イベントが続くことになるだろう。このようなデバイスは、あらゆる条件下でメモリスタとして機能するが、実用性は低くなる。

メモリスティブ体系

次メモリスティブ体系のより一般的な概念では、定義方程式は次のとおりであり、 ここでは入力信号であり、は出力信号であり、ベクトルはデバイスを説明する個の状態変数のセットを表し、そしてとは連続関数である。電流制御メモリスティブ体系の場合、信号は電流信号を表し、信号は電圧信号を表す。電圧制御メモリスティブ体系の場合、信号は電圧信号を表し、信号は電流信号を表す。

純粋なメモリスタはこれらの方程式の特殊なケースであり、つまりが電荷のみに依存()するとき、電荷は時間微分を介して電流に関係するためである。したがって、純粋なメモリスタの場合、 (すなわち、状態の変化率) は電流と等しいか、それに比例しなければならない。

ピンチ化ヒステリシス

メモリスタとメモリスティブ体系の結果生じる特性のうち1つが、ピンチ化ヒステリシス効果の存在である[50]。電流制御メモリスティブ体系の場合、入力は電流であり、出力は電圧であり、そして曲線の傾きは電気抵抗を表す。ピンチ化ヒステリシス曲線の傾きにおける変化は(ReRAMおよびその他の形式の2端子抵抗メモリの現象の中心である)異なる抵抗状態間のスイッチングを示す。高周波においては、メモリスティブ理論はピンチ化ヒステリシス効果が退化してしまうことを予測し、線形抵抗器を表す直線をもたらす。非交差ピンチ化ヒステリシス曲線の一部の種類 (タイプ-IIと示される) は、メモリスタによって説明することはできないことが証明された[51]。

メモリスティブ・ネットワークと回路相互作用の数学モデル

メモリスティブ・ネットワークの概念は蔡少棠によって1965年の彼の論文「メモリスティブ・デバイスと体系(Memristive Devices and Systems)」で初めて発表された。蔡は人間の脳の振舞いをシミュレートできるかもしれない人工ニューラル・ネットワークを構築する手段としてメモリスティブ・デバイスの利用を提案した。事実、回路におけるメモリスティブ・デバイスはキルヒホッフの法則による複雑な相互作用を持つ。メモリスティブ・ネットワークはメモリスタンスの特性を示す電子部品である、メモリスティブ・デバイスに基づく、人工ニューラル・ネットワークの一種である。メモリスティブ・ネットワークにおいて、メモリスティブ・デバイスは人間の脳のニューロンとシナプスの振舞いをシミュレートするために使用される。ネットワークは一連の重みを介して他の各層に接続される、メモリスティブ・デバイスの層から構成される。これらの重みはトレーニング・プロセス中に調整され、ネットワークが新しい入力データに対して学習と適応することを可能にする。メモリスティブ・ネットワークの利点の1つは、比較的シンプルで安価なハードウェアを使用して実装でき、これらを低コストの人工知能システムを開発するための魅力的な選択肢にする。また、より少ない電力で情報の格納と処理をできるため、従来の人工ニューラル・ネットワークよりもエネルギー効率が高い可能性もある。しかしながら、メモリスティブ・ネットワークの分野は、まだ開発の初期段階にあり、その能力と限界を完全に理解するには、さらなる研究が必要とされている。電圧発生器を直列に接続したメモリスティブ・デバイスのみの最も単純なモデルの場合、各デバイスのネットワークの内部メモリの進化を説明する、厳密な閉じた形式の方程式 (テンプレート:Ill2、CTDV)[52]が存在する。2つの抵抗値間のスイッチの(しかし現実的ではない)単純なメモリスタ・モデルの場合、(を伴う)Williams-Strukovモデルによって与えられる、次のような形式を取る一連の非線形結合微分方程式が存在する: ここで、は対角線上に要素を持つ対角行列であり、はメモリスタの物理パラメータに基づく。ベクトルは、メモリスタに直列に接続された電圧発生器のベクトルである。回路トポロジーは、グラフの回転行列(cycle matrix)という観点から定義される、射影作用素(projector operator) にのみ入る。この方程式はキルヒホッフの法則による相互作用の簡潔な数学的記述を提供する。興味深いことに、この方程式はリアプノフ関数や古典的なトンネル現象の存在など、ホップフィールド・ネットワークと共通する多くの特性を共有する[53]。メモリスティブ・ネットワークの文脈において、CTD(V)方程式は異なる動作条件下におけるメモリスティブ・デバイスの振舞いを予測するため、若しくは特定の用途向けメモリスティブ回路の設計と最適化をするために使用される。

拡張された(理論)体系

一部の研究者の中にはReRAMの振る舞いの説明におけるHPのメモリスタ・モデルの科学的な正当性に疑問を提起し[37][38]、そして拡張メモリスティブ・モデルを提案した[26]。

一例[54]では、級数展開時に入力信号の高次導関数を組み込んだ動的体系を含むことによってメモリスティブ・システム・フレームワークを拡張するよう試みており、 ここでは正の整数であり、は入力信号であり、は出力信号であり、 ベクトルはデバイスを説明する個の状態変数のセットを表し、そしてとは連続関数である。この方程式はメモリスティブ・システムとして同じゼロ交差ヒステリシス曲線を生成するが、しかしメモリスティブ・システムによって予測されるそれよりも異なる周波数応答を伴う。

別の例は、オフセット値を含む、予測されるゼロ交差ピンチ化ヒステリシス効果を破る観測されたナノバッテリー効果について勘定に入れることを提案している[26]。

ヒステリック(ヒステリシス的な)電流-電圧メモリスタの実装

ヒステリック電流-電圧曲線またはヒステリック電流-電圧曲線とヒステリック磁束-電荷曲線の両方を伴うメモリスタの実装が存在する[arXiv:2403.20051]。ヒステリック電流-電圧曲線を伴うメモリスタは電流と電圧の履歴に依存する抵抗を利用し、そしてそれらの簡素な構造、高エネルギー効率、そして高インテグレーション(en:integration, 完成? or 集積?)ゆえ、メモリー技術の未来にとっては良い前兆である[DOI: 10.1002/aisy.202200053]。

二酸化チタンメモリスタ

2007年にヒューレット・パッカードのテンプレート:Ill2によって実験的な固体版が報告された時、メモリスタへの関心が再燃した [55][56][57]。この論文は初めて、ナノスケール薄膜の振る舞いに基づくメモリスタの特性があるかもしれない固体デバイスを実証したものであった。このデバイスは、理論上のメモリスタに示唆されたように磁束を利用するでもなく、コンデンサと同じように電荷を蓄えるでもなく、代わりに電流の履歴に応じた抵抗を実現する。 HPのTiO2メモリスタにおける彼らの初期のレポートには引用されていないけれども、二酸化チタンの抵抗スイッチング特性は元々1960年代に述られていた[58]。

HPのデバイスは厚さ5nmの2つの電極(一方はチタン、他方は白金)の間に、薄い (50nm) 二酸化チタン膜からできている。当初は、二酸化チタン膜には2つの層があり、そのうちの1つは酸素原子がわずかに欠乏している。酸素空孔は電荷キャリアとして働き、空乏層の抵抗が非空乏層よりもはるかに低いことを意味する。電界が印加されると、酸素空孔はドリフトし (高速イオン伝導体 を参照されたし)、高抵抗層と低抵抗層の間の境界を変える。したがって膜全体の抵抗は、特定の(電流の方向を変えることで可逆的になる)方向にどれくらいの電荷が通過したかに依存する[18]。HPのデバイスはナノスケールでの高速イオン伝導を示すため、ナノイオン・デバイスと考えられる[59]

メモリスタンスはドープ層と空乏層の両方が抵抗に寄与する場合のみ表される。イオンがもはや移動できなくなるほどメモリスタに十分な電荷が通過するとき、デバイスはヒステリシス(状態)に入る。それは積分をすることを止め、むしろを上界に保ち、そしては固定される、したがって電流が逆流するまで定抵抗器としての機能を果たす。

しばらくの間、薄膜酸化物のメモリ応用は活発な調査が行われていた分野であった。IBMは2000年にウィリアムズによって述べられたものに似ている構造物に関する論文を公開した[60]。サムスンはウィリアムズによって述べられたものに似た酸化物空孔ベースのスイッチに関する米国特許を取得している[61]。

2010年4月に、HP研は彼らが1ns (~1GHz) スイッチング時間で動作し、そして3nm四方サイズの実用的なメモリスタを手に入れたと発表し[62]、それは技術の未来にとっては良い前兆である[63]。これらの密度では、それは現在のサブ25nmフラッシュメモリ技術に簡単に匹敵する可能性がある。

二酸化ケイ素メモリスタ

1960年代には早くも二酸化ケイ素のナノスケール薄膜においてメモリスタンスが報告されているようである[64]。

しかしながら、ケイ素中におけるヒステリック・コンダクタンスにメモリスティブ効果との関連性が確認されたのは2009年になってからである[65]。 さらに最近(2012年初)、Tony Kenyon、Adnan Mehonicそして彼らのグループは、導電性原子間力顕微鏡を使用して電気バイアス下での酸素の動きを直接調べ、そしてその結果得られた導電性フィラメントを画像化し、酸化ケイ素薄膜における抵抗スイッチングは欠陥操作された二酸化ケイ素における酸素空孔フィラメントの形成によるものであることを明確に実証した[66]。

高分子メモリスタ

2004年に、KriegerとSpitzerは、機能する不揮発性メモリセル作成するために必要なスイッチング特性と保持(力)を改善した高分子(ポリマー)の動的ドーピングと無機誘電体様材料を述べた[67]。彼らは電極と(電極からのイオン抽出を強化する)活性薄膜の間の不動態層を使用した。この不動態層のように(イオン抽出場の大幅な削減を可能にする)高速イオン伝導体を利用することを可能にする。

2008年7月に、ErokhinとFontanaは、最近発表された二酸化チタンメモリスタよりも先に高分子メモリスタを開発したと主張した[68]。

2010年に、Alibart、Gamrat、Vuillaumeら(et al.)[69]は、メモリスタとして振る舞い[70]そして生物学的スパイキング・シナプスの主な振る舞いを示す新しいハイブリッド有機/ナノ粒子デバイス (略: テンプレート:Ill2: ナノ粒子有機メモリ・電界効果トランジスタ) を発表した。このデバイスは、シナプスタ (シナプス・トランジスタ) とも呼ばれ、神経にインスパイヤされた回路 (パブロフ学習を示す連想記憶) を実証するために使用された[71]。

2012年に、Crupi、PradhanそしてTozerらは、有機「イオンベース」メモリスタを利用し神経シナプス記憶回路を作り出すための概念実証設計を述べた[72]。そのシナプス回路は、忘却に基づく不活化と同様に学習について長期増強を実証した。回路の格子を使用して、光のパターンが格納されたのちに思い出された。これは輪郭や動きのある線などの視覚信号を処理する時空間フィルターとして機能する、一次視覚野にあるV1ニューロンの挙動を真似する。

2012年に、Erokhinと共著者らは、高分子メモリスタに基づく学習と適応について能力を備えた確率的3次元行列を実証した[73]。

積層メモリスタ

2014年に、Bessonovら(et al.)は、プラスチックホイル上の銀電極の間に挟まれているテンプレート:Ill2/MoS2ヘテロ構造から成るフレキシブル・メモリスティブ・デバイスを報告した[74]。この製造方法は、二次元層状遷移金属ダイカルコゲナイド (TMD) で使われる印刷および溶液処理技術に完全に基づく。メモリスタは機械的に柔軟性があり、光学的に透明で、そして低コストで生産される。スイッチのメモリスティブな振る舞いは、顕著なメモキャパシティブ効果を伴うことが判明した。高いスイッチング性能は、テンプレート:Ill2が実証され、そして機械的変形に対する持続可能性が斬新なコンピューティング技術において生物学的神経システムの魅力的な性質を模倣することを保証する。

原子抵抗器

原子抵抗器(Atomristor)は、原子的に薄いナノマテリアルまたは原子シートでメモリスティブな振る舞いを示す電気デバイスとして定義されている。2018年に、テキサス大学のテンプレート:Ill2・グループのGeとWuら(et al.)は、垂直テンプレート:Ill2 (MIM) デバイス構造に基づく単層テンプレート:Ill2 (MX2, M = Mo, W; そして X = S, Se) 原子シートで普遍的なメモリスティブ効果を最初に報告した[75]。この研究は後に、約0.33nmの最薄メモリ材料である、六方晶窒化ホウ素単分子膜まで拡張された[76]。これら原子抵抗器は、成形フリー・スイッチングそして単極性と双極性動作の両方を提供する。スイッチング挙動は、さまざまな導電性電極(金、銀そしてグラフェン)をともなう、単結晶膜や多結晶膜に見られる。原子的に薄いTMDシートは、CVD/MOCVDによって調製され、低コスト製造を可能にする。その後、低「オン」抵抗と巨大なオン/オフ比を活かして、MoS2またはh-BN(六方晶-窒化ホウ素)原子抵抗器に基づく高性能ゼロパワーRFスイッチが証明され、5G、6GそしてTHz通信とおよび(その)接続システム向けといったメモリスタの新たな用途を示唆している[77][78]。2020年に、導電性仮想点メカニズムの原子論的理解は、テンプレート:Ill2の論文で解明された[79]。

強誘電体メモリスタ

強誘電体メモリスタ[80]は、2つの金属電極の間に挟まれた薄い強誘電体バリアに基づく。接合の全域にわたって正または負の電圧を印加することで強誘電体物質の分極を切り替えることは、2桁台の抵抗値変動をもたらす可能性がある: テンプレート:Nowrap (この効果は「トンネル電気抵抗」と呼ばれる)。一般に、分極は急には切り替わらない。その逆転は、逆の分極を有する強誘電体領域の核形成と成長を通じて徐々に起こる。この過程で、抵抗値はRONでもROFFでもなく、その中間である。電圧を周期的に変えると、強誘電体領域の形態が徐々に発展し、抵抗値の微調整が可能になる。強誘電体メモリスタの主な利点は、メモリスタ応答速度の設計を監督する方法を提供することで強誘電体領域のダイナミクスを調整できるということ、そして抵抗値変動は純粋に電子現象によるものであり、材料構造への大きな改変が伴なわないため、デバイスの信頼性を向上させるということである。

カーボン・ナノチューブ・メモリスタ

2013年に、Ageev、Blinovら(et al.)[81]は、カーボン・ナノチューブ(CNT)の束を走査型トンネル顕微鏡で研究している際に、垂直に一列に整列させたCNTに基づく構造物においてメモリスタ効果が観測されることを報告した。

その後、CNTメモリスティブ・スイッチングはナノチューブが不均一な弾性ひずみΔL0を有する場合に観察される[82]ことが発見された。これは、ひずんだСNTのメモリスティブ・スイッチング・メカニズムは不均一な弾性ひずみの形成と続いて起こる再分布、及び外部電界 E(x,t) の影響下にあるナノチューブにおける圧電界Edefに基づくということが示された。

生体分子メモリスタ

バイオマテリアルが人工シナプスにおける利用について評価されており、そしてニューロモルフィック・システムにおける応用についてポテンシャルが示されている[83]。特に、人工シナプス・デバイスとしてのコラーゲンベースのバイオメモリスタを利用することの実現可能性が調査されており[84]、リグニンに基づくシナプス性デバイスが電圧の符号に依存する連続的な電圧掃引を伴う電流の上昇または下降を実証した一方[85]、さらに天然の絹繊維がメモリスティブ特性を実証した;[86] 生体分子に基づくスピンメモリスティブ・システムも研究されている[87]。

2012年に、テンプレート:Ill2と共著者たちは初めて、高感度バイオセンサーの実現を目指す生体分子メモリスタを提案した[88]。それ以後、いくつかのメモリスティブ・センサーが実証されている[89]。

スピン・メモリスティブ体系

スピントロニクス・メモリスタ

ChenとWang、ディスク-ドライブ・メーカー、シーゲイト・テクノロジーの研究員たちは磁気メモリスタの見込みがある物の3つの例を述べた[90]。あるデバイスにおいて、デバイスのあるセクションにおける電子のスピンが、もう1つのセクションにおけるそれら(電子のスピン)から異なる方向に指し示す時に抵抗は生じ、2つのセクションの間の境界、「領域壁」を作り出す。デバイスに流れ込む電子は一定の(デバイスの磁化状態を変える)スピンを持っている。磁化の変化は (順番に) 領域壁を移動させ、抵抗を変化させる。研究の趣旨は、テンプレート:Ill2によるインタビューにつながった[91]。初の磁気トンネル接合におけるスピン流による領域壁運動に基づくスピントロニクス・メモリスタの実験的証明が2011年に載った[92]。

磁気トンネル接合におけるメモリスタンス

磁気トンネル接合が、外因性 (酸化還元反応、電荷捕獲/デトラップおよび障壁内でのエレクトロマイグレーション) と内因性 (テンプレート:Ill2)の両方の、いくつかの潜在的に相補的なメカニズム等を通じてメモリスタとして機能を果たすことが提案されている。

外部的メカニズム

1999年から2003年にかけて実施された調査に基づき、Bowenら(et al.)は、双安定(性)のスピン依存状態[93](抵抗スイッチング)を賦与された磁気トンネル接合 (MTJ) について2006年に実験結果を発表した。MTJは、ハーフメタリック酸化物LSMOと強磁性金属CoCr電極を分離するSrTiO3 (STO) トンネル障壁より成る。MTJの通常の2つの(電極磁化の平行または反平行整列によって特徴づけられた)デバイス抵抗状態は、電界を印加することによって変更される。電界がCoCrからLSMO電極に印加される時、トンネル磁気抵抗 (TMR) 比は正である。電界の方向が逆転される時、TMR(比)は負である。両方の場合において、約30%のTMRの巨大な増幅が発見されている。(Julliereモデル内では)ハーフメタリックLSMO電極から完全にスピン偏極した電流が流れるため、この正負変換は効果的なSTO/CoCr界面のスピン偏極における正負変換を暗示する。この多状態効果の起源は、観測されたCrの障壁への移行と、その酸化(作用)の状態次第である。TMRの正負変換は、ランドスケープ(横置き)STO/CoCr界面にてCrOx酸化還元反応によって引き起こされた変遷からトンネリングまでと同様に、状態の修飾からSTO/CoCr界面密度まで生み出すことができる。

MgOベースのMTJ内でMgOベースのメモリスティブ・スイッチングに関する報告が2008[94]~09年[95]頃から出現した。観測されたメモリスティブ効果を説明するために絶縁MgO層内の酸素空孔のドリフトが提案された一方[95]、別の説明は酸素空孔の[96]局所的な状態における電荷捕獲/デトラップと、スピントロニクスにおける[97]その影響である可能性が提案された。これはデバイスの(強誘電性[98]あるいはテンプレート:Ill2[99]のような固有の特性を備えた複合酸化物類を活用する)メモリスティブ動作において酸素空孔が、どういう役割を果たすのか理解することの重要性を強調する。

本質的メカニズム

MTJの磁化状態はテンプレート:Ill2によって制御され(そして従って)この固有の物理的メカニズムを通して、メモリスティブな振る舞いを示しうる。このスピン・トルクは接合の中を流れる電流によって誘発され、そしてMRAMを達成する効率的な手段につながる。しかしながら、接合の中を流れる電流の時間の長さは必要とされる電流の量を決定する、すなわち換言すれば、電荷が基本変数である[100]。

本質的 (スピン伝達トルク) および外部的 (抵抗スイッチング) メカニズムの組み合わせは自然に状態ベクトルx = (x1,x2 (ここでx1は電極の磁性状態を述べ、x2はMgO障壁の抵抗状態を示す))によって述べられる2次のメモリスティブ体系につながる。この場合、x1の変化は (スピン・トルクは高電流密度に起因するため) 電流制御型である一方、x2の変化は (酸素空孔のドリフトは高電界に起因するため) 電圧制御型である。メモリスティブ磁気トンネル接合における両方の効果の現存はナノスケール・シナプス-ニューロン・システムの着想につながった[101]。

スピン・メモリスティブ体系

メモリスティブな振る舞いについて根本的に異なるメカニズムがPershinとテンプレート:Ill2によって提案された[102][103]。著者らはテンプレート:仮リンクとテンプレート:Ill2によって定義されたようなメモリスティブ体系の幅広いクラスに属する半導体スピントロニクス構造の特定の種類を証明している[2]。そのような構造におけるメモリスティブな振る舞いのメカニズムは(ナノ構造におけるイオン輸送よりも(むしろ)、より便利なコントロールを与える)電子スピン自由度に完全に基づく。(電圧などの) 外部制御パラメーターが変更される時に、電子スピン偏極の調整はヒステリシスに起因する拡散(過程)と緩和過程のために遅らされる。この結果は半導体/強磁性体境界面におけるスピン抽出の研究において予期されたが[104]、しかしメモリスティブな振る舞いの見地からは述べられていない。短いタイムスケール上、これらの構造は、ほぼ理想的なメモリスタとして振る舞う[5]。この結果は半導体スピントロニクスの応用可能範囲を広げ、そして未来の実用的な応用に一歩前進させる。

自律志向型チャネル・メモリスタ

2017年に、Kris Campbellは正式に自律志向型チャネル (SDC: Self-Directed Channel) メモリスタを発表した[105]。SDCデバイスは世界中の研究者、学生そしてエレクトロニクス愛好家にとって商業的に利用可能な最初のメモリスティブ・デバイスである[106]。SDCデバイスは製造後、即座に使用可能である。Ge2Se3活性層にて、Ge-Ge等極結合などが発見され、およびスイッチングを引き起こす。3つの層は上部タングステン電極の直下に、堆積中に一緒に混ぜ合わさり共同で銀-ソース層を形成する、Ge2Se3/Ag/Ge2Se3からなる。SnSe層はこれら2つの層の間にあり、銀-ソース層が活性層と直接接触しないことを保証する。高温では銀は活性層には移行せず、(と同時に)また活性層は約テンプレート:Convertの高いガラス遷移温度を維持するため、デバイスは著しくより高い(加工)処理温度および動作温度を、それぞれテンプレート:Convertおよび少なくともテンプレート:Convertを持つ。これら処理および動作温度はフォトドープまたは熱的にアニールされる必要があるS-ベースのガラス類 (例えばGeS) を含む、ほとんどのイオン伝導性カルコゲン化物デバイスのタイプよりも高い。これらの要因はSDCデバイスにテンプレート:Convertでの長時間連続動作を含む、広範囲の温度にわたる動作を可能にする。

ヒステリック(ヒステリシス的な)磁束-電荷メモリスタの実装

ヒステリック電流-電圧曲線とヒステリック磁束-電荷曲線の両方を伴ったメモリスタの実装が存在する[arXiv:2403.20051]。ヒステリック電流-電圧曲線とヒステリック磁束-電荷曲線の両方を伴ったメモリスタは磁束と電荷の履歴に依存するメモリスタンスを利用する。それらのメモリスタはデータ転送なしに算術論理ユニットおよびメモリ・ユニットの機能性を融合できる[DOI: 10.1002/adfm.201303365]。

時間積分化・成形フリー・メモリスタ

時間積分化・成形フリー (TiF: Time-integrated Formingfree) メモリスタは(正および負のバイアス範囲における2つの区別可能な分岐を伴う)ヒステリック磁束-電荷曲線を明らかにする。そしてTiFメモリスタもまた(正および負のバイアス範囲における2つの区別可能な分岐を伴う)ヒステリック電流-電圧曲線を明らかにする。TiFメモリスタのメモリスタンス状態は磁束と電荷の両方によって制御されうる[DOI: 10.1063/1.4775718]。TiFメモリスタは初めて2011年にハイデマリー・シュミットと彼女のチームによって実証された[DOI: 10.1063/1.3601113]。このTiFメモリスタは、金属性伝導電極(一方は(純)金、他方は白金)の間のBiFeO3薄膜から構成される。TiFメモリスタのヒステリック磁束-電荷曲線は(正および負のバイアス範囲における一方の分岐(書き込み分岐)において)その勾配を連続的に変化させ、およびならびに(正および負のバイアス範囲における一方の分岐(読み込み分岐)において)定数勾配を持つ[arXiv:2403.20051]。蔡少棠によると[Reference 1: 10.1.1.189.3614]磁束-電荷曲線の勾配はメモリスタのメモリスタンスまたはその内部状態変数に対応する。TiFメモリスタは2つの読み込み分岐において定数メモリスタンスを伴う、およびならびに2つの書き込み分岐において再構成可能メモリスタンスを伴うメモリスタとして考えられる。TiFメモリスタのヒステリック電流-電圧曲線を述べる物理的メモリスタ・モデルは2つの読み込みおよびならびに2つの書き込み分岐における静的と動的内部状態変数を実装する[arXiv:2402.10358]。

非線形メモリスタの静的および動的内部状態変数は線形、非線形、そして超越さえ(例えば指数または対数)入力-出力関数を表す非線形メモリスタにおける動作を実装するために使用されうる。

微小電流 – 微小電圧範囲におけるTiFメモリスタの輸送特性は非線形である。この非線形性は基本的な以前および現在のフォン-ノイマン(型)コンピュータの算術論理ユニットにおけるビルディングブロックの、すなわち換言すれば、真空管およびトランジスタの微小電流 – 微小電圧範囲における非線形特性とよく似ている。真空管およびトランジスタとは対照的に、ヒステリック磁束-電荷メモリスタ(すなわち換言すれば、TiFメモリスタ)の信号出力は(信号出力をメモリに格納する前に動作電力を消される時に)失われない。従って、ヒステリック磁束-電荷メモリスタはデータ転送なしで算術論理ユニットおよびメモリ・ユニットの機能性を融合すると言われる[DOI: 10.1002/adfm.201303365]。ヒステリック電流-電圧メモリスタの微小電流 – 微小電圧範囲における輸送特性は線形である。これは「なぜヒステリック電流-電圧メモリスタはメモリ・ユニットをよく設立されるのか」および「なぜそれらはデータ転送なしで算術論理ユニットおよびメモリ・ユニットの機能性を融合できないのか」を説明する[arXiv:2403.20051]。

潜在的な用途

メモリスタは相変わらず研究室の珍品であるが、(将来はともかく)今までのところでは、いかなる商業用途をも得るには不十分な数しか製造されなかった。この大量利用可能性の欠如にもかかわらず、Allied Market Researchによれば、メモリスタ市場は2015年に320万ドルの価値であった、そして当時は2022年までに7900万ドルの価値になると予測されていた[107]。事実、2022年には1億9000万ドルの価値であった[108]。

メモリスタの潜在的な用途には超伝導量子コンピュータ用アナログ・メモリが入っている[13]。

メモリスタは潜在的に(DRAMに似たアクセス時間とともにハードドライブよりも大きいデータ密度を可能にし、両方のコンポーネントを置き換える)不揮発性ソリッド-ステート・メモリに仕立て上げられ得る[109]。HPは平方センチメートルあたり100ギガビットを収容可能なクロスバー・ラッチ・メモリを試作した[110]、そして(最大1000層または1ペタビット/cm3からなる)スケーラブル3Dデザインを提案した[111]。2008年5月にHPは、そのデバイスが現在のところDRAMの約10分の1の速度に到達していることを報告した[112]。そのデバイスの抵抗は、格納された値に影響を及ぼさないようにするために、交流で読み出される[113]。2012年5月に、そのアクセス時間が(同時代のフラッシュメモリよりも100倍近く速い)90ナノ秒に改善されたことが報告された。と同時にエネルギー消費(量)はフラッシュメモリによって消費される「それ」のたった1パーセントであった[114]。

メモリスタは、プログラマブル・ロジック[115]・信号処理[116]、超解像イメージング[117]・テンプレート:Ill2[118]、制御システム[119]、再構成可能コンピューティング[120]、テンプレート:Ill2[121]、ブレイン=コンピュータ・インタフェース[122]そしてRFID[123]に用途がある。メモリスティブ・デバイスは潜在的に、CMOS-ベースの論理演算の置換を可能にする、ステートフル論理推論に使用され[124](、)いくつかの初期の研究などは、この方向性で報告されている[125][126]。

2009年に、LCネットワークとメモリスタからなるシンプルな電子回路[127]は、単細胞(微)生物の適応行動についての実験をモデル化するために使用された[128]。周期的パルスの訓練の対象となった、(細胞質におけるチャネルの粘稠度が周期的環境変化に呼応する、変形菌モジホコリの振る舞いに似た)この回路は学習し、次に来るパルスを予期するということが証明された[128]。そのような回路の応用には(例えば)パターン認識を含むかもしれない。DARPAのSyNAPSEプロジェクトは(ボストン大学ニューロモルフィックス研とのコラボレーションで)HP研に資金を提供したことは、メモリスティブ体系に基づいているかもしれないニューロモルフィック・アーキテクチャを開発してきている。2010年に、テンプレート:Ill2とChandlerは、MoNETA (Modular Neural Exploring Traveling Agent) モデルを述べた[129]。MoNETAは仮想(エージェント)およびロボットエージェントを強化するためにメモリスティブ・ ハードウェアを使用して全脳回路を実装する最初の大規模ニューラルネットワークモデルである[130]。アナログ・ソフト・コンピューティング・システムの構築におけるメモリスタ・クロスバー構造の応用はMerrikh-BayatとShourakiによって実証された[131]。2011年に、ファジー入出力端子を伴うアナログ・メモリスティブ・テンプレート:Ill2・コンピューティング・システムを作成するために、どうメモリスタ・クロスバーをファジー論理と組み合わされ得るのか、彼らは証明した[132]。学習はヘビアン学習則からインスピレーションを受けたファジー関係の作成に基づく。

2013年に蔡少棠はメモリスタが及ぼす広範囲にわたる複雑な現象と応用そして、どう「それらを不揮発性アナログ・メモリとして使えるか」及び「古典的な馴化(現象)及び学習現象の模倣ができるのか」をはっきり示すチュートリアルを公開した[133]。

派生デバイス

メミスターとメモトランジスタ

テンプレート:Ill2とテンプレート:Ill2はメモリスタ機能を含むトランジスタ-ベース・デバイスである。

メモキャパシタとメミンダクタ

2009年に、テンプレート:Ill2、Pershin、そして蔡は、メモリスティブ体系についての概念を(特性がシステムの状態と履歴に依存する)メモキャパシタとメミンダクタという形で容量性素子と誘導性素子に拡張し[134]、Di VentraとPershinによって2013年にさらに拡張された[23]。

メモフラクタンスとメモフラクタ、2次と3次のメモリスタ、メモキャパシタとメミンダクタ

2014年9月に、Mohamed-Salah Abdelouahab、Rene Lozi、そして蔡少棠は、分数階微分を使った1-、2-、3-、及びn-次メモリスティブ素子の一般理論を発表した[135]。

歴史

メモリスタの存在は1971年にテンプレート:仮リンクの論文で指摘されていたが、対応する物理現象が発見されず、メモリスタは長い間実現されることはなかった。しかし、2008年に米テンプレート:仮リンクにより二酸化チタンの薄膜を用いたメモリスタが開発され、第4の回路素子として注目を集めることとなった。

記憶素子としてはフラッシュメモリより高速・低消費電力であり[136]、DRAMより安価で省電力であるという性質を持っていると言われ、両方を置き換える可能性がある。面積あたりの記憶容量もフラッシュメモリと比べて2倍にでき、また放射線による影響も受けないというメリットがある[136]。

2010年4月には、メモリスタが論理演算装置としても使用できることを確認したとHPが発表。演算装置と記憶素子を単一のデバイスに統合できるため、より小型でエネルギー効率の良いデバイスを開発できる可能性が示された[136]。

HPは2020年までの完全な形での商品化を目指している。

少史

先達

サー・ハンフリー・デービーが1808年という昔にメモリスタ効果によって説明されうる最初の実験を実施したと一部の人に言われている[21][137]。しかしながら関連した性質を持って構築された最初のデバイスは(テンプレート:Ill2と呼ばれる早期の人工ニューラルネットワークの回路素子を述るためにバーナード・ウィドローによって1960年に作られた造語)メミスター(すなわち換言すれば、メモリ抵抗器)であった。数年後(1968年に)ArgallがTiO2の抵抗スイッチング効果を証明する論文(後にメモリスタの証拠があるとヒューレットパッカード出身の研究者らによって主張されたものでもある)を公開した[58]テンプレート:Citation needed。

理論的説明

蔡少棠は1971年に彼の新しい2端子回路素子を仮定した。第4の基礎的な回路素子として、それは電荷と磁束鎖交との間の関係によって特徴づけられた[5]。5年後、彼と彼の生徒「姜城模」はリサジュー曲線において電流テンプレート:Snd対テンプレート:Snd電圧の振る舞いを特徴づけるメモリスタの理論と(ゼロ交差の性質を含む)メモリスティブ体系を一般化した[2]。

21世紀

2008年5月1日に、Strukov、Snider、Stewart、そしてWilliamsはNature 誌にて、ナノスケール・システムとメモリスタで見つけた2端子抵抗スイッチングの振る舞いの間のつながりを特定したとする論文を公開した[18]。

2009年1月23日に、Di Ventra、Pershin、そして蔡は、(特性がシステムの状態と履歴に依存する)容量性素子と誘導性素子(すなわちキャパシタとインダクタ)にメモリスティブ体系についての概念を拡張した[134]。

2014年7月に、(テンプレート:Ill2、テンプレート:Ill2、テンプレート:Ill2、そしてテンプレート:Ill2出身の研究者から成る)MeMOSat/LabOSatグループ[138]は、メモリ・デバイスを低軌道に投入した[139]。それ以来、異なるデバイスで7回のミッション[140]を、テンプレート:Ill2のÑu-Sat低軌道衛星のオンボード(機内)で、実験を行っている[141][142]テンプレート:Clarify。

2015年7月7日に、Knowm Incは、自律志向型チャネル (SDC: Self-Directed Channel) メモリスタの商業化を発表した[143]。これらのデバイスは、相変わらず少量生産に留まっている。

2018年7月13日に、メモリスタ評価ペイロードを飛ばすためにMemSat (Memristor Satellite: メモリスタ衛星) が打ち上げられた[144]。

テンプレート:Anchors2021年に、MITのテンプレート:Ill2とMartin Bazantは、ニューロモルフィック・コンピューティングにおける酸化リチウム-ベース・メモリスタを含む、バッテリー電極におけるそれらの使用を越えたリチウムの応用を調査するために「リチオニクス(Lithionics)」研究プログラムを始めた[145][146]。

2023年5月に、TECHiFAB GmbH[https://techifab.com/]は、TiFメモリスタの商業化を発表した[arXiv: 2403.20051, arXiv: 2402.10358]。これらのTiFメモリスタは、相変わらず少量~中量生産に留まっている。

Science誌2023年9月号に、中国人科学者テンプレート:Ill2ら(et al.) は、エッジ・コンピューティング・アプリケーション向けに最適化された、機械学習及び人工知能タスクの速度と効率性を劇的に向上させるように設計された、メモリスタ-ベース集積回路の開発とテストを述べた[147]。

関連項目

- テンプレート:Ill2

- テンプレート:Ill2

脚注

参考文献

- テンプレート:Cite journal

- テンプレート:Cite journal

- テンプレート:Cite book

- テンプレート:Cite book

- テンプレート:Cite journal

- テンプレート:Cite journal

- テンプレート:Cite journal

- テンプレート:Cite journal

- テンプレート:Cite journal

- テンプレート:Cite journal

- テンプレート:Citation

外部リンク

以下全部英語

- テンプレート:YouTube

- メモリスタ論文の対話型データベース (2013年)

- テンプレート:Cite news

- 「蔡少棠: 電球vs.グーグル(謹製・囲)碁選手」テンプレート:Snd(ポーランド語版) メモリスタの創造主、蔡少棠とのインタビュー

- 「蔡少棠: 電球vs.グーグル(謹製・囲)碁選手」テンプレート:Snd(英語版) メモリスタの創造主、蔡少棠とのインタビュー

テンプレート:Electronic components テンプレート:新技術テンプレート:Normdaten テンプレート:Physics-stub

- ↑ テンプレート:Cite journal

- ↑ 2.0 2.1 2.2 2.3 2.4 テンプレート:Citation

- ↑ 3.0 3.1 引用エラー: 無効な

<ref>タグです。「Pershin_2018」という名前の注釈に対するテキストが指定されていません - ↑ 引用エラー: 無効な

<ref>タグです。「Kim_2019」という名前の注釈に対するテキストが指定されていません - ↑ 5.0 5.1 5.2 5.3 テンプレート:Cite journal

- ↑ テンプレート:Citation

- ↑ 7.0 7.1 テンプレート:Cite book

- ↑ テンプレート:Cite report

- ↑ テンプレート:Citation

- ↑ テンプレート:Citation

- ↑ テンプレート:Cite book

- ↑ テンプレート:Citation

- ↑ 13.0 13.1 テンプレート:Citation

- ↑ テンプレート:Cite book

- ↑ 15.0 15.1 テンプレート:Citation

- ↑ テンプレート:Citation

- ↑ 17.0 17.1 17.2 17.3 テンプレート:Cite journal

- ↑ 18.0 18.1 18.2 18.3 18.4 18.5 18.6 テンプレート:Cite journal

- ↑ テンプレート:Citation

- ↑ テンプレート:Cite journal

- ↑ 21.0 21.1 テンプレート:Citation

- ↑ 引用エラー: 無効な

<ref>タグです。「Meuffels_2012」という名前の注釈に対するテキストが指定されていません - ↑ 23.0 23.1 引用エラー: 無効な

<ref>タグです。「DiVentra_2013」という名前の注釈に対するテキストが指定されていません - ↑ テンプレート:Cite journal

- ↑ テンプレート:Cite journal

- ↑ 26.0 26.1 26.2 26.3 26.4 テンプレート:Citation

- ↑ 27.0 27.1 テンプレート:Cite journal

- ↑ テンプレート:Cite journal

- ↑ テンプレート:Citation

- ↑ テンプレート:Cite journal

- ↑ テンプレート:Citation

- ↑ テンプレート:Citation

- ↑ テンプレート:Citation

- ↑ テンプレート:Cite web

- ↑ テンプレート:Cite journal

- ↑ テンプレート:Citation

- ↑ 37.0 37.1 テンプレート:Citation

- ↑ 38.0 38.1 テンプレート:Citation

- ↑ テンプレート:Citation

- ↑ 40.0 40.1 40.2 テンプレート:Cite arXiv

- ↑ 41.0 41.1 41.2 41.3 41.4 テンプレート:Citation

- ↑ 42.0 42.1 テンプレート:Cite journal

- ↑ テンプレート:Cite book

- ↑ テンプレート:Citation

- ↑ テンプレート:Citationテンプレート:Dead link

- ↑ テンプレート:Cite journal

- ↑ テンプレート:Citation

- ↑ テンプレート:Citation

- ↑ テンプレート:Citation

- ↑ テンプレート:Citation

- ↑ テンプレート:Citation

- ↑ テンプレート:Cite journal

- ↑ テンプレート:Cite journal

- ↑ テンプレート:Cite arXiv

- ↑ テンプレート:Citation

- ↑ テンプレート:Citation

- ↑ テンプレート:Citation

- ↑ 58.0 58.1 テンプレート:Citation

- ↑ 。 テンプレート:Citation

- ↑ テンプレート:Citation

- ↑ Stefanovich, Genrikh; Cho, Choong-rae; Yoo, In-kyeong; Lee, Eun-hong; Cho, Sung-il; Moon, Chang-wook (2006) "Electrode structure having at least two oxide layers and non-volatile memory device having the same" テンプレート:US Patent

- ↑ テンプレート:Citation

- ↑ テンプレート:Citation

- ↑ テンプレート:Cite journal

- ↑ テンプレート:Citation

- ↑ テンプレート:Cite journal

- ↑ テンプレート:Citation

- ↑ テンプレート:Cite arXiv

- ↑ テンプレート:Cite journal

- ↑ テンプレート:Cite journal

- ↑ テンプレート:Cite journal

- ↑ テンプレート:Citation

- ↑ テンプレート:Cite journal

- ↑ テンプレート:Citation

- ↑ テンプレート:Cite journal

- ↑ テンプレート:Cite journal

- ↑ テンプレート:Cite journal

- ↑ テンプレート:Cite journal

- ↑ テンプレート:Cite journal

- ↑ テンプレート:Citation

- ↑ テンプレート:Cite journal

- ↑ テンプレート:Cite journal

- ↑ テンプレート:Cite journal

- ↑ テンプレート:Cite journal

- ↑ テンプレート:Cite journal

- ↑ テンプレート:Cite journal

- ↑ テンプレート:Cite journal

- ↑ テンプレート:Cite journal

- ↑ テンプレート:Cite journal

- ↑ テンプレート:Citation

- ↑ テンプレート:Cite web

- ↑ テンプレート:Cite journal

- ↑ テンプレート:Cite journal

- ↑ テンプレート:Cite journal

- ↑ 95.0 95.1 テンプレート:Citation

- ↑ テンプレート:Citation

- ↑ テンプレート:Citation

- ↑ テンプレート:Citation

- ↑ テンプレート:Citation

- ↑ テンプレート:Citation

- ↑ テンプレート:Citation

- ↑ テンプレート:Cite web

- ↑ テンプレート:Citation

- ↑ テンプレート:Citation

- ↑ テンプレート:Citation

- ↑ テンプレート:Citation

- ↑ テンプレート:Cite web

- ↑ テンプレート:Cite web

- ↑ 引用エラー: 無効な

<ref>タグです。「Kanellos」という名前の注釈に対するテキストが指定されていません - ↑ テンプレート:Citation

- ↑ テンプレート:Citation

- ↑ テンプレート:Citation

- ↑ テンプレート:Citation

- ↑ テンプレート:Citation

- ↑ Snider, Gregory Stuart (2004) "Architecture and methods for computing with reconfigurable resistor crossbars" テンプレート:US patent

- ↑ Mouttet, Blaise Laurent (2006) "Programmable crossbar signal processor" テンプレート:US Patent

- ↑ テンプレート:Cite journal

- ↑ Snider, Greg (2003) "Molecular-junction-nanowire-crossbar-based neural network" テンプレート:US patent

- ↑ Mouttet, Blaise Laurent (2007) "Crossbar control circuit" テンプレート:US Patent

- ↑ Pino, Robinson E. (2010) "Reconfigurable electronic circuit" テンプレート:US Patent

- ↑ テンプレート:Cite journal

- ↑ Mouttet, Blaise Laurent (2009) "Memristor crossbar neural interface" テンプレート:US Patent

- ↑ Kang, Hee Bok (2009) "RFID device with memory unit having memristor characteristics" テンプレート:US Patent

- ↑ テンプレート:Cite journal

- ↑ テンプレート:Cite journal

- ↑ テンプレート:Cite book

- ↑ テンプレート:Citation

- ↑ 128.0 128.1 テンプレート:Citation

- ↑

テンプレート:Cite web

テンプレート:Cite journal - ↑ テンプレート:Citation

- ↑ テンプレート:Citation

- ↑ テンプレート:Cite arXiv

- ↑ テンプレート:Cite journal

- ↑ 134.0 134.1 テンプレート:Citation

- ↑ テンプレート:Citation

- ↑ 136.0 136.1 136.2 テンプレート:Cite web

- ↑ テンプレート:Citation

- ↑ テンプレート:Citation

- ↑ テンプレート:Cite news

- ↑ テンプレート:Citation

- ↑ テンプレート:Cite web

- ↑ テンプレート:Cite news

- ↑ テンプレート:Cite news

- ↑ テンプレート:Cite news

- ↑ テンプレート:Cite web

- ↑ テンプレート:Cite web

- ↑ テンプレート:Cite journal